## Cu2-xSe-CdSe 光起電力素子 B - 19

## ◆川博義 宫下和雄 和田正信"(窗山大工学部\* 東北大工学部\*\*) 勉 0大竹

前用の報告と同様に、真空墜着法により CuarSe-CalSe 光起電力素子を作製した。今田は、光起 まえがき 電力の大きな素子を得らためKなされる CuzzSe茎着後の熱処理と特性の変化の関係を調べ、熱処理 によな接合の変化について考察したので報告すな。

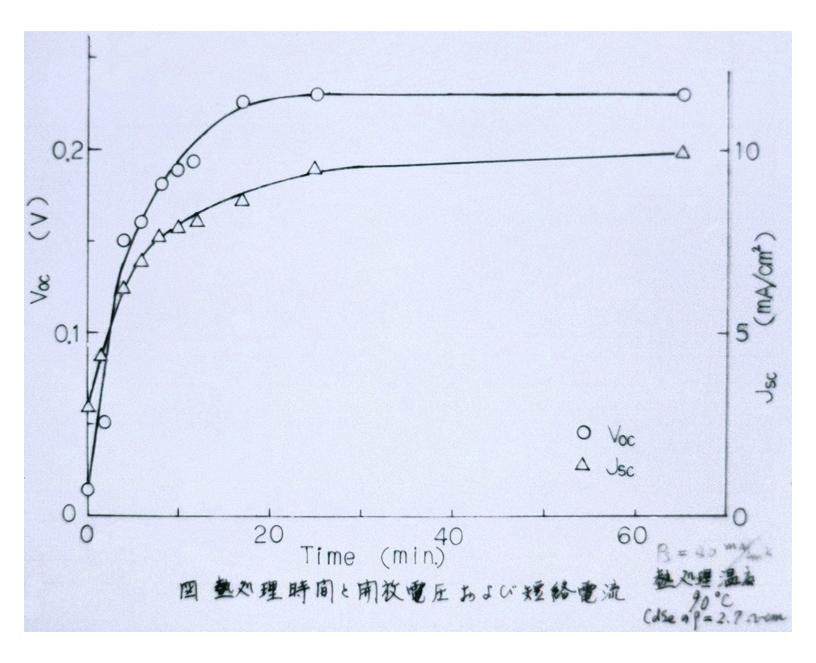

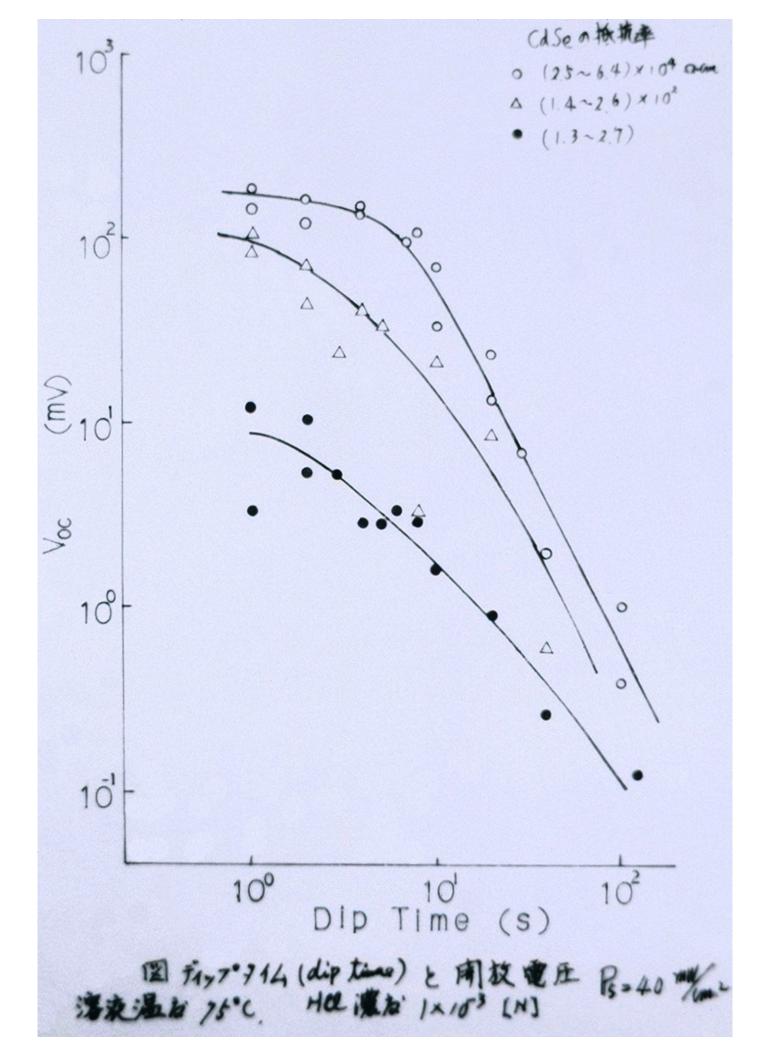

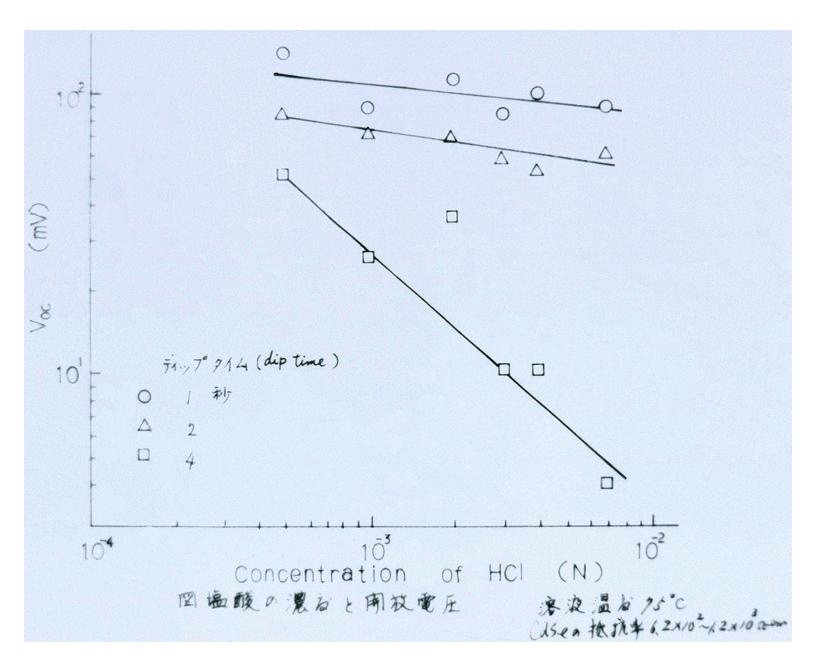

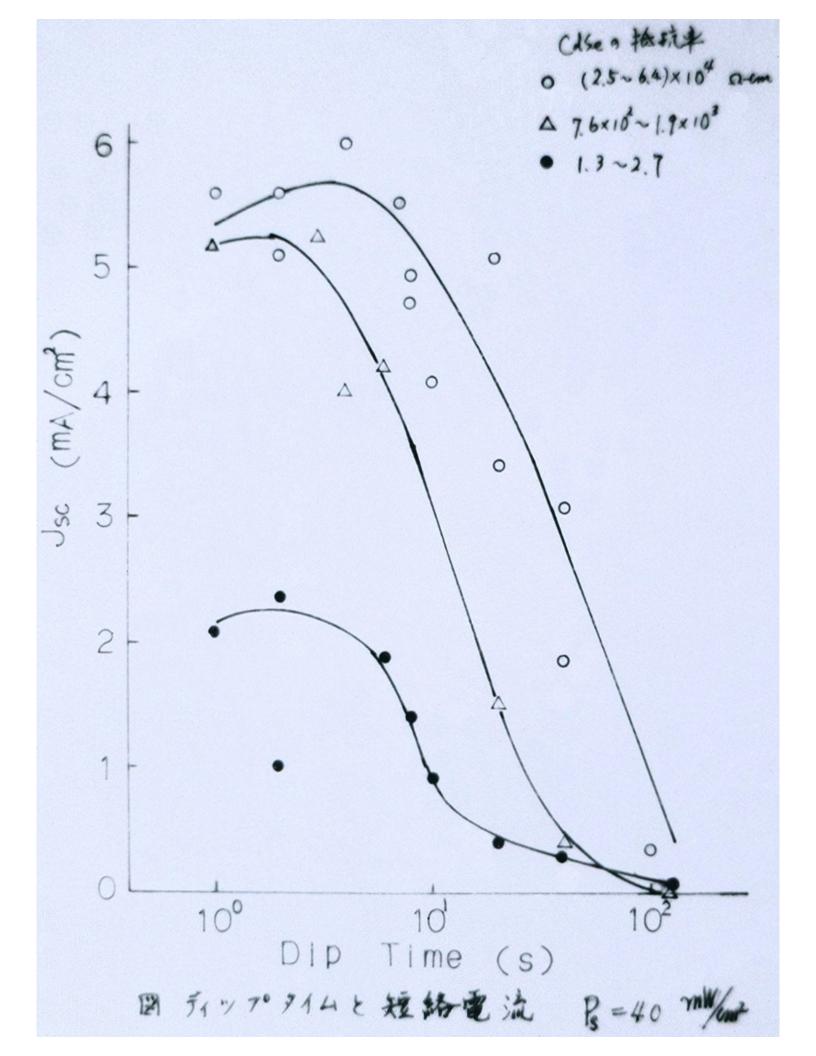

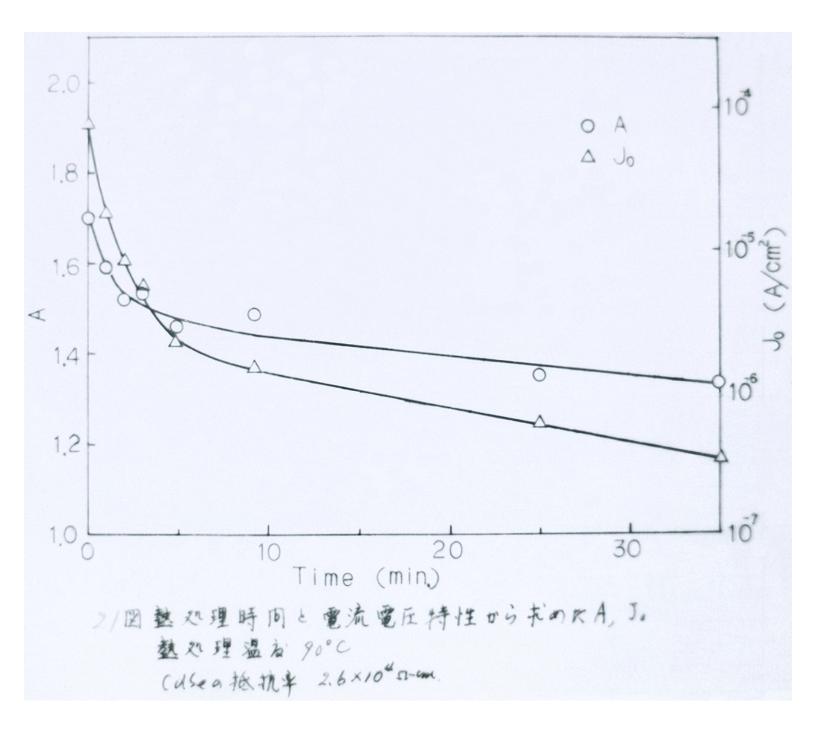

実験結果. 光起電力の大きな素子を作るためには、ColSe基板を加熱しながらCusaSeを基着動か(図1)あ ないは、CuzaSe 蓋着後に越処理を施さなければならない(图2)ことがわれた。 図1と図2から、ColSeの抵抗率が 大きい方が、Curase 茎着中 K CdSe 基板を加熱する方法K あいては、加熱温なが低くてもよく、Curase 茎着後K熱 処理する方法にあいては短時間でよいことがわかった。図3はCurySe茎着後に数処理する方法によって作製した 素子の, 塾処理Kよる分光特性(短絡電流)の変化である。 CASの限界波長(130 m/4)付近で感激が急激K浜少 した。また、表処理の素子では長波長側(200m/4付近)の威なが少なく、 CdSeo抵抗率 0 ~103 s-m 充分K熱処理したあとでは、短波長側(500m/1/地)の威友が減少することが Δ ~10<sup>4</sup> Ω-cm 0.2 わかった。 図4は 熱処理時間と電流-電圧特性の 関係である。未処理 E のときはオーム性に近いものが、就処理によって発流性が現われることが ЧH わか、た、得られた素子の変換効率に約3%(光泳:タンブステンランプ)であった。 ₩0.1 さらK,光記電力K対する境界面の影響を調べるためK,別の方法で接 す 合を作製し比較した。すなわち、CdSe膜をCuttrン溶液に愛してCdSe表面に Ħ Cuarse層を作り、その素子の特性を調べた。熱処理の効果Kのいては図2と同じ 0 ' 0 50 100 150 傾向が得られ,電流-電圧特性, 開放電圧, 短絡電流, 发换效率も CuzaSe o 温 な (°C) 芝着によって作業した素子と大きな差はなかった。 11. CuzzSe基着時の基板温台と南放電圧 考察、图3でColSeの限界波長で分光威なが急い減少ないとから主として Colse中で吸収された光が光記宅カバ寄与していると思られる。また障壁を界 03 領域で発生したキャリアドけが光起電力に寄与すると考えると、図2と図3は次のよ 302 うい説明される。未処理の状態ではCASe中の障壁電界領域は光の吸收領域よ りも狭く、長波長(クロッル付近)の光は障壁電界領域を通過するので長波長の威能 Calsea抵抗率 2.5×105 0-cm が少なく光起会力は少ない。載処理を施すと、LKWK障壁電界領域が広くなて ※01年 5.8×104 長裕長の威なが増加する。障壁電界領域が光の吸収領域を越えると、光はすべ 📼 7.3 x 103 16.9 × 102 て障壁電界領域で吸収されるが、表面近くで発生したもりアは再結合等K& 0 5 間 10 て失われ,短波長(500m/4付近)の威なが減りする。 時 (分) このことから、CuzzaSe茎着後、熱処理KよってColSe中K高抵抗層ができ、それが 图2. 数处理時間と 南放電圧 (温な110℃) 障壁電界も形成していると思め 0 未処理 12-れる。また,化学的大作製した素子 △ 2分翅処理 1.4 単14) (mp/m) の特性との比較から、光起きかは • 14 1.2 (元、) 刻处理温友 境界面の状態にはあまり依存せ 流 0.8 ず、むしろ ColSe中KできK障壁 流 電界領域に起因していなと思い 0.4 R bib -0.8 -04 络  $\cap$ 化学的K作製した素子の実 0,2 0.4 題 電圧(V) 験に)しては本学卒業生の • 末饥理 -02 △ 4分熱処理 大浦利雄氏の援助を得たい 0 ■ /4分 0.4 500 400 600 700 800 に謝意を表する あの理温友 110°C (m,u) 沷 長 (dseo.故抗学 5.8×104-5-00 文献 1) 大竹如 新知 图4. 電流電圧特性 图3. 分光特性 (短鋒電流)

44年 電気四等北陸連大手稿 44

A speaker, Tsutomu Otake\*\*, presented a paper "Cu2-xSe-CdSe Photovoltaic cells\*" at Joint conference of Hokuriku chapter of four Electrical Societies in 1970.

\* The world first research paper regarding the Cu<sub>2-x</sub>Se-CdSe Photovoltaic cells.

\*\* A lecturer in department of electronic engineering, faculty of engineering, Toyama university (University of Toyama later on), PhD in electrical engineering of Tohoku University.

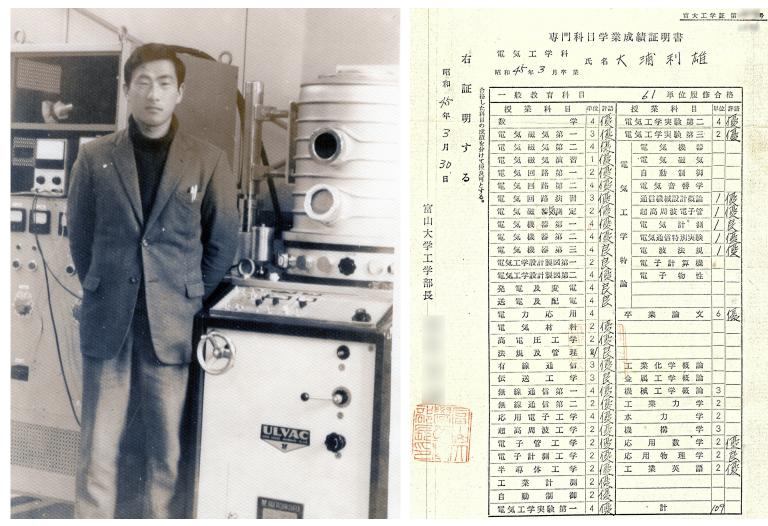

I was fortunate because Dr. Tsutomu Otake mentored my entire graduation research and FET.

When I was a 4th grader of Toyama University, I tentatively made a Cu<sub>2-x</sub>Se-CdSe photovoltaic cell (solar cell) on a glass plate under suggestion of lecturer Tsutomu Otake and professor Kazuo Miyashita. One of working samples achieved energy conversion efficiency of 3%\*.

The procedure\*\* I newly examined was;

- (1) Fabricate under heat treatment

- (2) Dry after dipping observing replacement reactions\*\*\*

- (3) Rinse by pure water

\* The 3% efficiency was measured according to the calculation between the output power density of 3 mW/cm<sup>2</sup> and the solar energy density of 100 mW/cm<sup>2</sup> at Toyama University Takaoka campus clear sunny day in March, 1970.

\*\* I was awfully surprised when the samples after rinse and dry exhibited a rectification characteristic and output electric power as the solar cells in December, 1969.

Heating the samples near coal stove seemed to be one of heat treatments essential for making the  $Cu_{2-x}$ Se-CdSe solar cells because the treatment made hetero p-n junctions to generate the electric powers by lights. Placing the rinsed samples of the cells near heat generating coal stove was derived from my serendipity.

\*\*\* A n-type semiconductor CdSe (Cadmium Selenium) thin film layer vapor-deposited on a chrominum thin film layer vapor-deposited on the glass plate is dipped into hydrochloric acid including Cu+ (Copper) ions in order to spawn replacement reactions of Cd atoms in a surface of the CdSe thin film layer to make a p-type semiconductor Cu<sub>2-x</sub>Se thin layer on the CdSe thin film layer.

Five pages slides attached reflect the experiment results performed for my graduation research titled "Cu<sub>2-x</sub>Se-CdSe Solar cells based on replacement method". It was referred by the paper listed at the first page.

$Cu_{2-x}$ Se-CdSe solar cell functional improvement applied by heat treatment (60 minutes at 90°C) I invented compared to no heat-treatment (no dip time) are the followings.

- Power generation effectiveness improved 57.8 times.

- Output power based on the Voc (Open circuit voltage) exhibited 17 times more.

- Short circuit current density Jsc exhibited 3.4 times more.

See slides attached.

When I was a 4th grader, I joined Miyashita laboratory led by professor Kazuo Miyashita, who was one of coauthors of the paper, in order to study semiconductor further more because I was interested in the semiconductor technologies lectured by him when I was a 3rd grader. It definitely triggered me joining NEC. Fortunately, I was able to study MOS Feild Effect cells in the Miyashita laboratory and was able to make Cu<sub>2-x</sub>Se-CdSe Photovoltaic cells (Solar cells) for my graduation research.

Based upon the actual results done at university, I requested top executives of semiconductor and IC sales division concerning job transfer from sales to engineering full-heartedly when interview done in April, 1970.

As a result, I started assisting engineers who were designing MOS LSIs for calculators in consumer product design group of circuit design department, IC division.

Then, I moved to the same design group in June, 1971 and awfully pleased to start designing MOS LSIs myself. More fortunately I met with Mr. Tetsuji Oguchi and work with him therein.

I took charge of the design of various E/D MOS LSIs for calculators sold substantial amount.

(1) µPD277C (First appearance of P-channel metal gate E/D MOS LSI in NEC)

3 million pieces of µPD277Cs were shipped to Sharp.

µPD276C/278C, derivatives of µPD277C, were shipped to Canon, Omron, Citizen, Calcomp and so on.

(2) µPD977C/577C (Second generation of E/D MOS LSI in NEC)

5 million pieces of  $\mu$ PD977Cs and 577Cs were shipped to Casio.

- Achieved lowest power dissipation of maximum 19.9mW and the smallest die size of 3.615mm square in NEC P-channel metal gate MOS LSIs for calculators of the day.

Toshio Oura at university lab

Graduation grades